AMD Ryzen 9050 APU 官方文件疑似流出:最高搭載 16 個 Zen 5 核心、40 個 RDNA 3+ 圖形單元、60 TOPS AI 性能

AMD Ryzen 9050 APU 疑似官方文件流出,揭露 Zen 5 架構完整規格

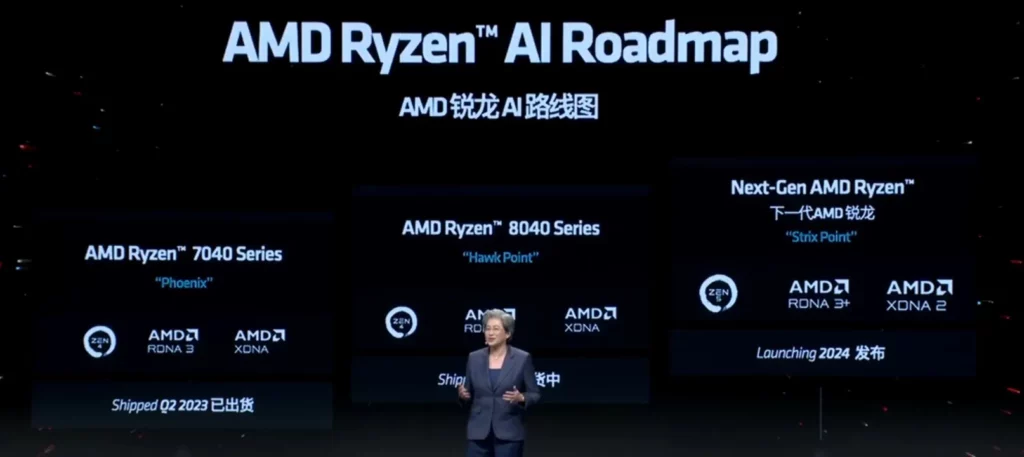

近期,一份據稱是 AMD 官方文件的資料流出,其中包含了 AMD 採用 Zen 5 架構的 Ryzen 9050 系列 APU(即代號 Strix 與 Strix Halo)的詳細資訊,曝光其下一代行動裝置產品線的完整平台細節。

AMD Strix 與 Strix Halo APU 將為 Ryzen 行動裝置產品線帶來重大更新

這份曝光內容來自 HKEPC,他們在 X 網站上發現一位名為 Izzukias 的用戶發布的 AMD 官方文件。原始貼文目前已被刪除,但該科技媒體仍掌握了不少訊息,甚至分享了 Strix 與 Strix Halo 系列的規格頁面,這兩個系列將搭載次世代 Zen 5 CPU、RDNA 3+ 圖形核心和 XDNA 2 NPU 核心。

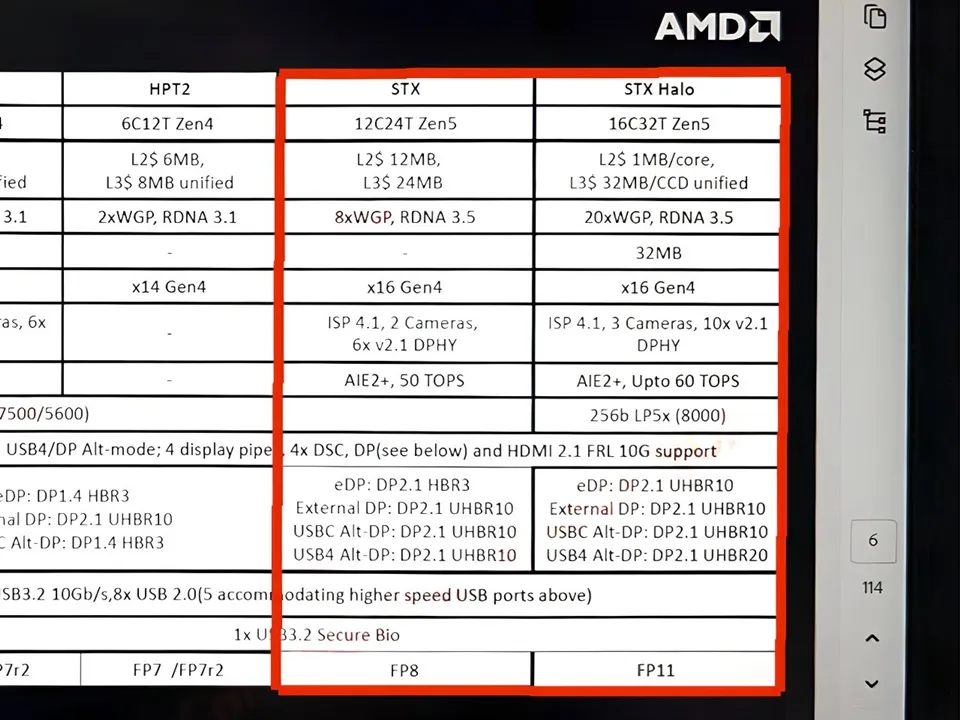

AMD Strix (1) APU 規格與平台詳情

首先,AMD Strix(Strix Point 1)系列將採用標準單晶片 APU 設計,這些晶片將在台積電 4nm 製程上製造,最高可提供 12 核心 24 執行緒。到目前為止,我們已經看到多個工程樣本流出。

在快取方面,這些 APU 將採用 12MB L2 快取(每個核心 1MB)和 24MB L3 快取,其中 8MB 分配給 Zen 5C,16MB 分配給 Zen 5 核心。這些晶片還將具有 32KB L1 指令快取,並增加到 48KB 的 L1 資料快取(Zen 4 上為 32KB)。APU 將提供 16 條 PCIe Gen 4 通道。

在記憶體支援方面,Ryzen Strix APU 將支援最高 LPDDR5-7500 與 DDR5-5600 記憶體,這是大多數主流筆電的標準配置。下一代 Ryzen AI 引擎則將提供高達 50 TOPS 的性能(XDNA 2)。AMD 內部似乎將其稱為 AIE2+ 或 AI Engine 2 Plus。

在圖形核心方面,將看到總共 8 個 RDNA 3+ WGP 或 16 個計算單元。到目前為止,我們已經看到這款晶片在早期樣品中的時脈頻率高達 2.6 GHz,因此最終晶片可能會達到 3 GHz 以上。這些 APU 曾被認為將配備 16MB 的 MALL 快取。所有 AMD Strix Point 1 APU 都將圍繞 FP8 插槽設計。據報導,Strix APU 系列的 TDP 將在 45-65W 之間,可以配置到 28W。

AMD Ryzen 9050 Strix Mono 的預期特性:

- Zen 5(4nm)單晶片設計

- 最高 12 核心混合配置(Zen 5 + Zen 5C)

- 24MB L3 快取 / 12MB L2 快取

- 16 個 RDNA 3+ 運算單元

- 支援 LPDDR5-7500 / DDR5-5600

- 整合 XDNA 2 引擎

- 最高 50 TOPS AI 性能

- 16 條 PCIe Gen4 通道

- 預計 2024 下半年發布

- FP8 平台(28W-65W)

AMD Strix Halo APU 規格與平台詳情

至於 AMD Strix Halo APU 將是採用多晶片設計的產品,最多使用 3 個晶片,2 個 CCD 和 1 個 IOD。這些晶片將配備最多 16 個 Zen 5 核心,具有 32 個執行緒,保留相同的 L1 和 L2 快取結構,因此最大可達 16MB L2 快取,而 L3 快取將增加到每個 CCD 32MB。因此,可以在頂級(兩個 CCD)晶片上看到高達 64MB 的 L3 快取。

在圖形核心方面,Strix Halo APU 將保留 RDNA 3+ 圖形架構,但將配備 20 個 WGP 或 40 個計算單元。此外,為了在多晶片設計中支援如此高階的圖形核心,IOD 上還將配備額外的 32MB MALL 快取,以消除這款超級圖形核心的頻寬瓶頸。

其他規格包括支援高達 LPDDR5x-8000(256-bit)記憶體,以及一個能夠提供高達 60 TOPS 性能的 AI「XDNA 2」NPU。Strix Halo APU 將圍繞最新的 FP11 平台,這些 APU 的 TDP 為 70W(cTDP 55W),並將支援高達 130W 的峰值功率。

AMD Ryzen 9050 Strix Halo 的預期特性:

- Zen 5 多晶片設計

- 最高 16 核心

- 64MB 共享 L3 快取

- 40 個 RDNA 3+ 運算單元

- 32MB MALL 快取(用於圖形核心)

- 256-bit LPDDR5X-8000 記憶體控制器

- 整合 XDNA 2 引擎

- 最高 60 TOPS AI 性能

- 16 條 PCIe Gen4 通道

- 預計 2024 年下半年發布

- FP11 平台(55W-130W)

在顯示方面,AMD Strix 和 Strix Halo APU 都將支援 eDP(DP2.1 HBR3)和外部 DP(DP2.1 UHBR10)、USBC Alt-DP(DP2.1 UHBR10)以及 USB4 Alt-DP(DP2.1 UHBR10)。Strix Halo 將支援高達 DP2.1 UHBR20。

AMD 預計將在本月下半月推出首款 Ryzen 9050「Strix Point」APU,此外,也可以期待在 2024 年 Computex 的 AMD 主題演講中獲得更多資訊。

歡迎加入我們的 Facebook 粉絲團,隨時掌握最新消息!

喜歡看圖說故事的話,也可以追蹤 Instagram 專頁!

我們也有 Google News 可以隨時 follow!